联系我们

芯片,数据掉电不会丢失。NOR FLASH 支持Execute On Chip,即程序能直接在FLASH 片内执行。这点和NAND FLASH 不一样。因此,在嵌入是系统中,NOR FLAS H 很适合作为启动程序的介质。NOR FLAS H 的读取和RAM很类似,但不可以直接进行写操作。对NOR FLAS H 的写操作需要遵循特定的命令序列,最终由芯片内部的控制单元完成写操作。所以,NOR FLASH一般是作为用于程序的

NOR的特点是芯片内执行(XIP, Execute In Place),这样应用程序能直接在FLASH闪存内运行,不必再把代码读到系统RAM中。NOR FLASH的传输效率很高,在1~4MB的小容量时具备极高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。

FLASH闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。任何FLASH器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。NAND FLASH器件执行擦除操作是十分简单的,而NOR FLASH则要求在进行擦除前先要将目标块内所有的位都写为0。

由于擦除NOR FLASH器件时是以64~128KB的块进行的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND FLASH器件是以8~32KB的块进行的,执行相同的操作最多只需要4ms。

执行擦除时块尺寸的不同进一步拉大了NOR FLASH和NADN FLASH之间的性能差距,统计表明,对于给定的一套写入操作(尤其是更新小文件时更多的擦除操作必须在基于NOR FLASH的单元中进行。

NAND FLASH的单元尺寸几乎是NOR FLASH器件的一半,由于生产的全部过程更为简单,NAND FLASH结构可以在给定的模具尺寸内提供更高的容量,也就相应地降低了价格。

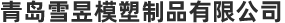

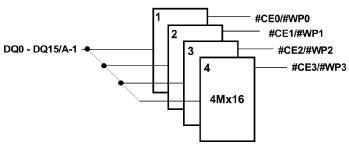

VDRF256M16是一款高集成度的静态随机存取存储器,其总含有256M bits。由于此芯片里面包含4个片选,每个片选含有1个Block,具体的内部结构见图1。这种结构不但大大的扩充了存储器的容量和数据位宽,而且还可以在应用时大量节省了PCB板的使用空间。从图1能够准确的看出,每个片选控制了每一Block的写保护信号#WP,另外芯片中的每一个Block的其他控制端口、地址线中的任一Block的结构框图,它主要由控制逻辑、存储整列等组成。下面为VD RF256M16的主要特性。

VDRF256M16芯片采用的是SOP封装工艺,整块芯片表面镀金,这样做才能够大幅度增强了芯片的抗干扰和抗辐射的能力,有利于该芯片能应用于航空航天等恶劣的环境。

VCC:+3.3V电源输入端。滤波的旁路电容应尽可能靠近电源引脚, 并直接连接到地;

#WE:此端为低时写入,为高时写无效,数据有效发生在相应地址有效之后的两个周期;

#WP/ACC[3..0]:最外的两个8KB的BOOT扇区保护状态。当电平为VIL时,此两扇区受保护,不可以进行擦除、编程操作;当电平为VIH时,取决于扇区保护状态,如此两扇区是受保护的则不可以进行操作,如未受保护则可进行擦除、编程操作;当电平为VHH时,将进入解锁旁路模式进入加速编程状态。此管脚不能悬空;

#CE[3..0]:低电平有效时选中该片,可通过两个片选信号选择四个Block,但两个片选信号不能同时选中;

#BYTE:字节/字模式选择。低电平为字节模式,DQ0~DQ7为数据端口,DQ8~DQ14为高阻状态,DQ15做LSB地址输入;高电平为字模式,DQ0~DQ15为数据端口;

VDRF256M16的软件操作可以分成两类: 普通读操作和命令操作。普通读操作格外的简单, 与RAM的读操作类似, 当#OE和#CE信号同时为低电平时, 即可从芯片读出数据。芯片的命令操作包括芯片的识别、字节编程、扇区擦除以及整片擦除等。这些操作分别由各自的软件操作命令序列来完成, 如表1所列。其中, BA为待编程字节的地址,Data为字节编程数据, SAX为待擦除扇区的地址。命令中的地址只有低15位有效, 高4位可任意设置为/ 00或/ 10。VDRF256M16的软件操作命令序列其实就是由一个或多个总线写操作组成的。以VDRF256M16的扇区擦除为例, 其操作的流程包括3个步骤: 第1步, 开启擦除方式,用表1中给出的第1至第5周期的总线步, 装载扇区擦除命令( 30H) 和待擦除扇区的地址, 用其对应的第6周期的总线步, 进行内部擦除。内部擦除时间最长为500ms。

总线写操作时,OE一定要保持为高电平, CE和WE应为低电平。地址和数据的锁存由CE和WE两个信号的边沿来控制。它们当中后出现的下降沿将锁存地址, 先出现的上升沿将锁存数据。

以VDRF256M16为核心,配合适当的控制信号,不仅能对存储器进行各种读写操作,而且还能够直接进行进一步的容量拓展。下面以该芯片在系统中的应用为例,介绍VDRF256M16在系统中的的硬件设计及各信号之间的时序关系。

硬件设计就是搭建合适的接口电路, 将VDRF256M16连接到微处理器的系统总线和微处理器的结构特性, 我们得知VDRF256M16的数据线、读、写等信号线可以很容易地连接到微处理器的系统总线 硬件电路原理图

微处理器接到指令,需将数据或程序存放至NOR FLASH时,微处理器首先会发送擦除指令将芯片进行擦除,具体的流程见图5。然后将数据或程序利用写指令写到FLASH中。当需要调取数据或程序指令的时候,需要从FLASH中调取程序,那就需要发送读指令到FLASH中,具体的流程见图6。

由于该设计的数据速度快,容量大,因此时序的配合很重要,这种配合不仅仅指单个Block中各信号与时钟的配合,同时也应考虑Block与Block之间的各信号之间的配合。当数据输入时地址和数据应在保持稳定;而数据输出时,地址也应保持稳定,这样才可以保证数据传输的可靠性及连续性。图5(读时序)和图6(写时序)为单片Block的控制时序图。从图中能够准确的看出:无论在读或写数据时,地址总线信号和控制信号在发送一段时间后,数据信号才能发送或者读取。所以在使用时,一定要注意时序上的延时。

本文所介绍的VDRF256M16是一款高速度、存储容量大的16位NOR FLASH存储器,总容量达到了256M,存储周期最大可达到90ns。16位的数据总线宽度能更好和更快速的采集和缓存数据。在实际的应用中,可作为高速缓存。但在使用的过程中必须要格外注意写入和读取数据的延时问题。另外,本芯片能在相当大的应用场景范围中使用,具有非常好的通用性,在需要高速大容量数据存储的场合的工程中比别的类型的存储器更有应用价值。